Hi-Res Static Screen Ram Schematics Overview By Michael Matte September 20, 2019

Subject: Re: Hi-Res Static RAM Project Update

From: MCM Design

Date: 9/20/2019, 5:37 PM

To: Adam Trionfo

The DWGs 1 thru 6 are finalized. You can post/forward these first 6 drawings as desired. DWG 5 as shown is for hi-res operation only with no multi-paging. The upcoming, additional drawings will be submitted to you as options to the original hi-res static screen RAM scheme (DWG 5). A user interested in building the new hi-res static screen RAM scheme can choose what option he/she wants to add on. There WILL be an option drawing for someone that just wants to operate the static screen RAM in low or hi-res with NO multi-paging. An option drawing will include and indicate any rewire necessary to DWG 4 or 5.

I just finished writing my overview. I will send it to you in a few minutes after I proof read it.

Bye. MCM

\_\_\_\_\_

Subject: Hi-Res Static RAM Project Update

From: MCM Design

Date: 9/20/2019, 5:54 PM

HI-RES STATIC SCREEN RAM SCHEMATICS OVERVIEW

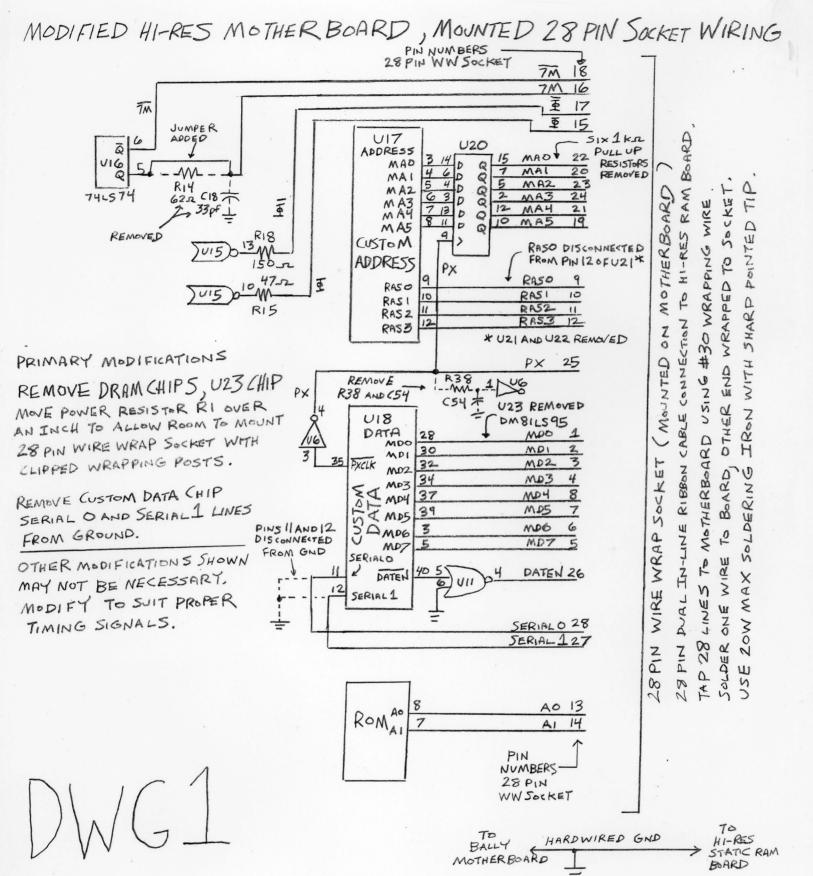

# DWG 1

Modified Hi-Res Motherboard, Mounted 28 Pin Socket Wiring Details the necessary motherboard modifications for hi-res operation. Includes 28 wiring lines from the motherboard to the 28 pin WW socket mounted on the motherboard.

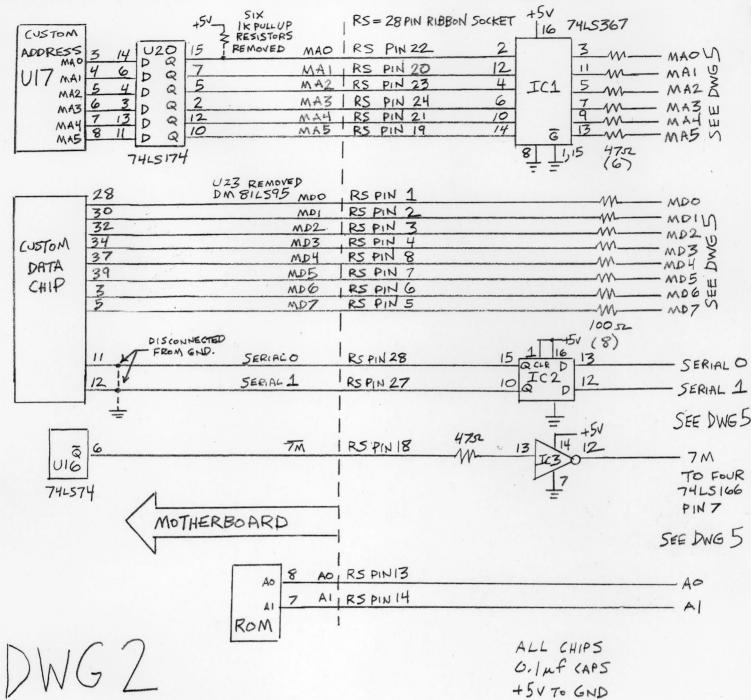

## DWG 2

Bally Motherboard To Hi-Res Screen RAM Board Shows some of the necessary interfacing from the 28 pin ribbon cable connection on the motherboard to the static screen RAM board scheme and the TV display scan circuitry detailed in DWG 5.

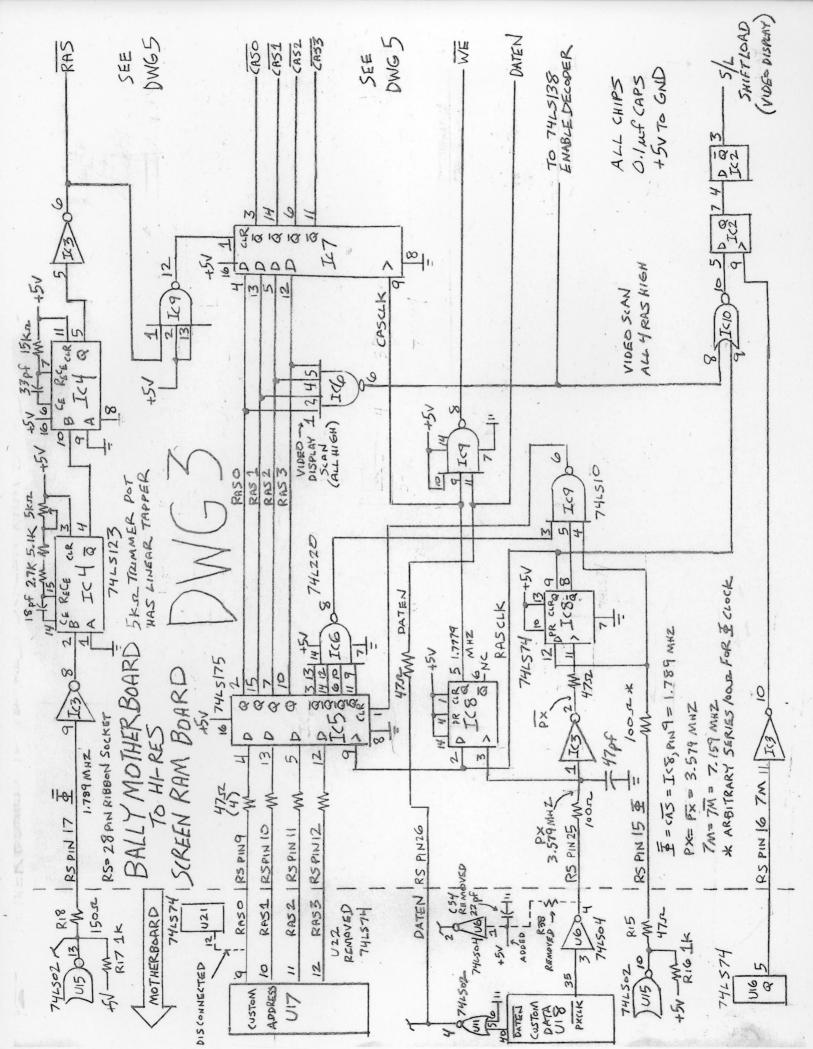

## DWG 3

Bally Motherboard To Hi-Res Screen RAM Board Shows additional interfacing and timing circuitry. Reference above DWG 2 description.

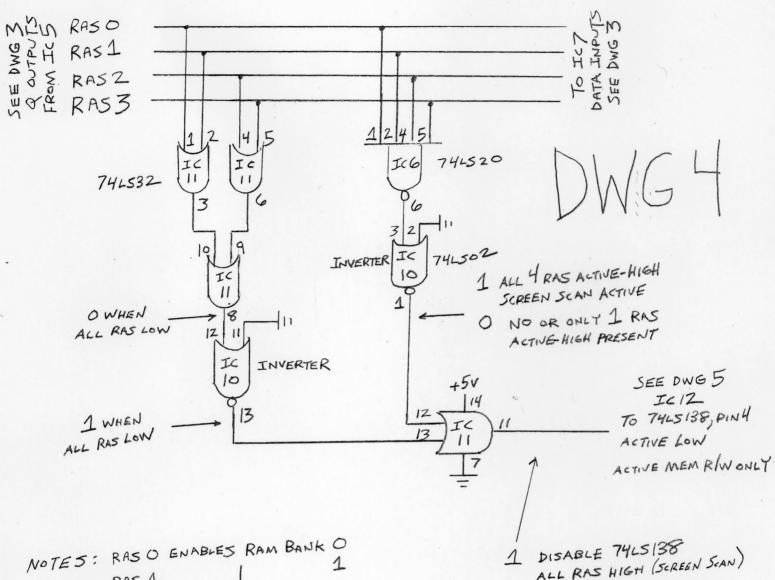

# DWG 4

74LS138 Enabler Decoder

Details the 74LS138 decoder for proper operation of the Z80 screen RAM read/write data bus and the TV display scan 32 bit read (scan) data bus.

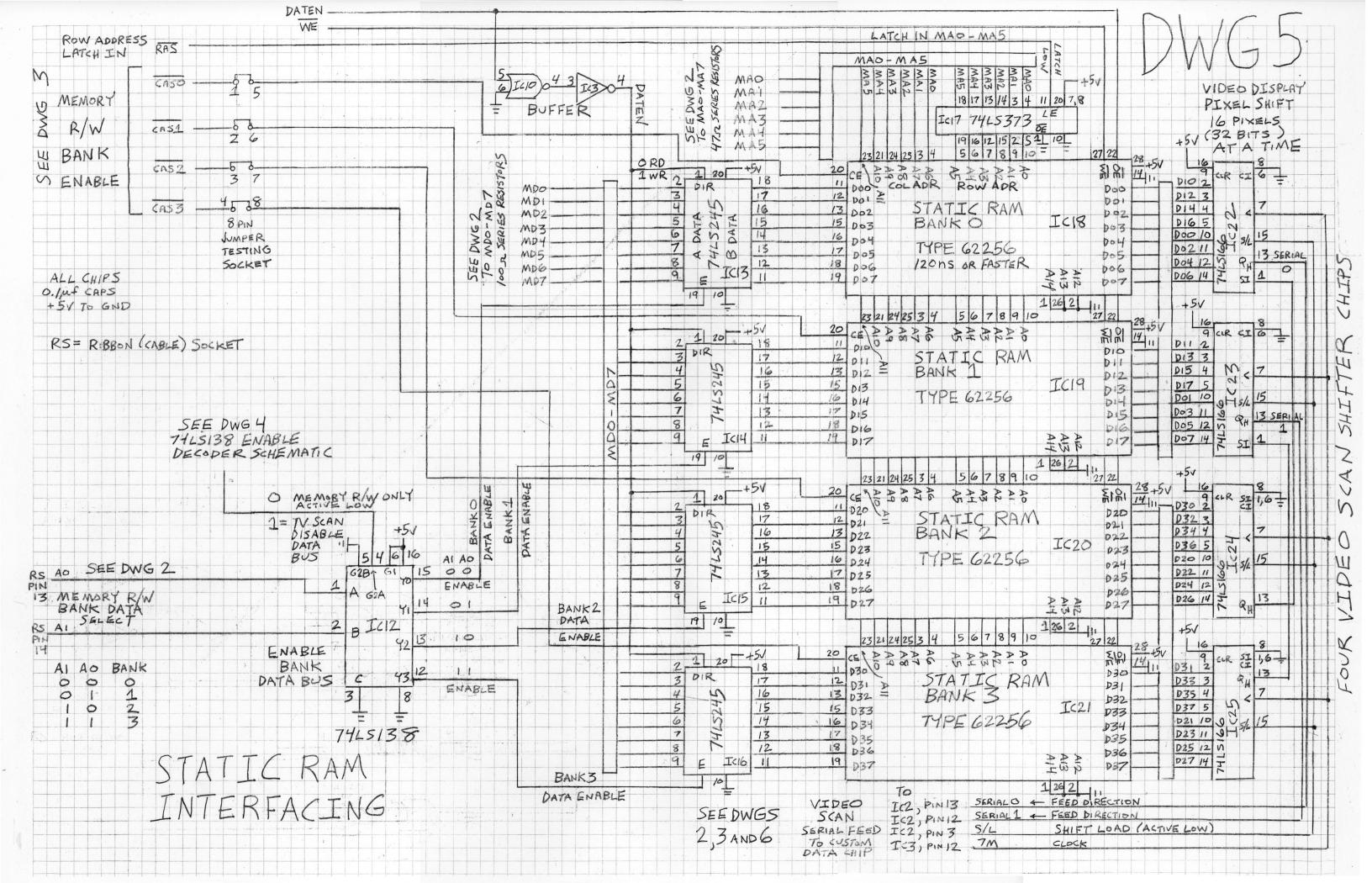

DWG 5

Static Screen RAM Interfacing

Details interfacing and all connections to the 4 banks of static screen RAM. Includes connections to the four 74LS166 TV display scan serial shifter chips.

User Notes

- 1. Check your static RAM pin layout for compatibility with the static RAM pin layout in DWG 5. If your static RAM pin layout is NOT compatible, wire your RAM to suit proper operation (or purchase compatible chips) and revise your version of DWG 5 for future reference.

- 2. DWG 5 as shown is wired for hi-res operation only with no multi-paging. To manually run this DWG 5 scheme in low-res, remove the IC12 chip 74LS138 from its socket. Add a jumper wire from the socket pin 15 to gnd pin 8. This jumper enables the Bank 0 RAM data bus for low-res operation only and "floats" (disables) the IC14, IC15 and IC16 data buses.

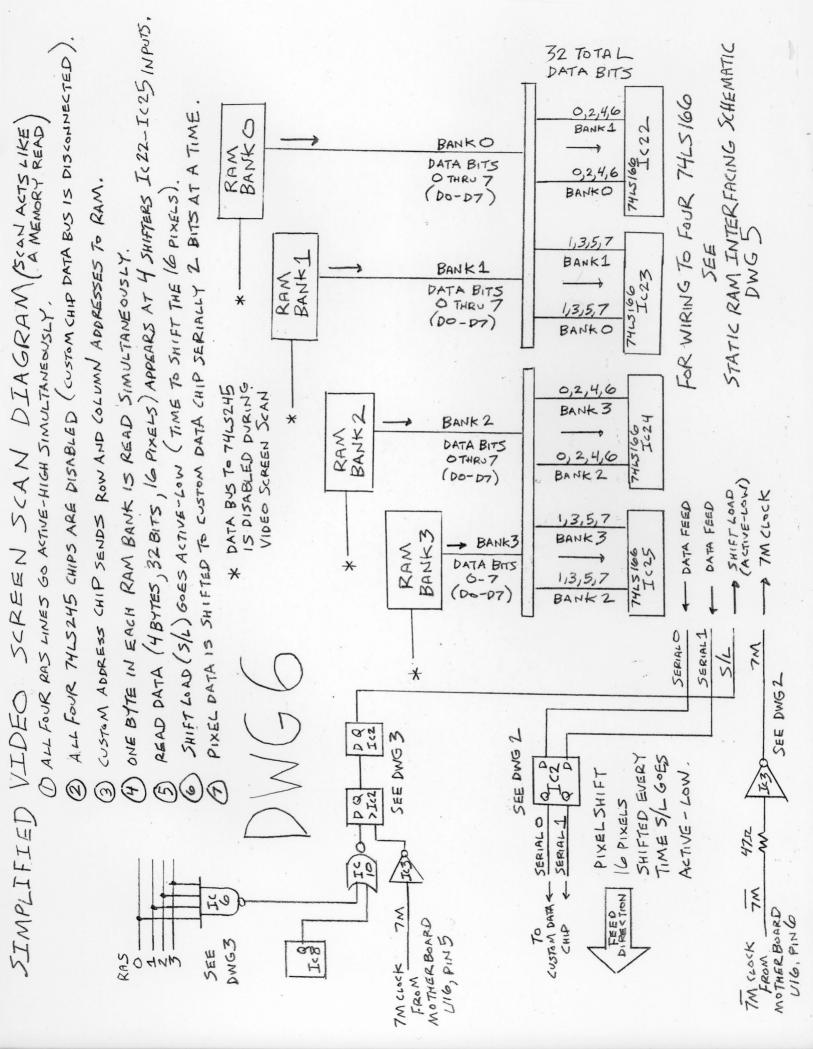

#### DWG 6

Simplified Video Screen Scan Diagram

The entire TV (video) screen scan circuitry is spread out over drawings 2,3 and 5. DWG 6 lays out the entire scan scheme in this one drawing 6, attempting to simplify the scheme so a user can grasp how the scanning scheme functions. A brief operation description is also included. For more details, reference the doc "A Description of the Bally Professional Arcade Video Hardware and Associated Coin-Operated Hardware" by Anthony J. Miller, which is archived on the Bally Alley website. This doc details the screen scan operation for the coin-op arcade Seawolf II. The scheme in DWG 6 is a variation of the scan scheme used in the DataMax UV-1R computer, which is documented on the Bally Alley website in MCM Design's original hi-res upgrade package 3. The original hi-res upgrade by MCM Design utilized dynamic RAM (DRAM) for it's hi-res screen RAM scheme.

Bye. MCM

# BALLY MOTHER BOARD TO HI-RES SCREEN RAM BOARD

# 7415138 ENABLE DECODER ENABLE ONLY WHEN A SINGLE R/W RAS IS ACTIVE-HIGH

NOTES: RAS O ENABLES RAM BANK O

RAS 1

RAS 2

RAS 3

ONE ACTIVE-HIGH RAS SELECTS SPECIFIC BANK FOR A MEMORY R/W,

ALL 4 RAS LINES ARE ACTIVE—HIGH

SIMULTANEOUSLY FOR A SCREEN SCAN,

HBYTES (16 PIXELS) ARE SCANNED AT ONE TIME,

LOADED INTO FOUR 74LS 166 CHIPS AND

SHIFTED SERIALLY INTO CUSTOM DATA CHIP

USING THE TWO SERIAL O AND SERIAL 1 LINES,

1 DISABLE 74LS (38 ALL RAS HIGH (SCREEN SCAN) OR ALL RAS LOW (INACTIVE)

O ENABLE 74LS 138

ACTIVE ONLY WHEN A

SINGLE R/WACTIVE-HIGH PULSE

15 PRESENT.

ALL CHIPS O. Inf CAPS +SV TO GND